# Analysis, Design and Control of Switching Capacitor Based Buck-Boost Converter

Mummadi Veerachary, *Senior Member, IEEE*, and Vasudha Khubchandani Dept. of Electrical Engineering, Indian Institute of Technology Delhi, New Delhi, INDIA *E-mail: mvchary@ee.iitd.ac.in*

Abstract— A switching-capacitor based buck-boost converter (with common ground) for point of load applications is proposed in this paper. It is capable of operating in stand-alone buck or boost mode in addition to its primary operation of performing the buck-boost conversion. The striking feature of the proposed converter is low source current ripple content irrespective of its mode of operation (buck-boost, buck, or boost). Firstly, feasible pulse width modulation (PWM) schemes for the proposed converter are identified and thereafter the corresponding circuit performance analysis, steady-state analysis and state-space modelling is established. Through steady-state analysis, voltage gain expressions are formulated and equations defining L-C components are derived in terms of their ripple quantities. The state-space models are used to formulate small-signal analysis and to obtain the relevant transfer functions required in the controller design. A voltage-mode/current-mode controller is designed, with a trade-off in bandwidth, to control the proposed converter and transit it from buck to boost mode or vice-versa seamlessly. A 30 ~ 55 Watt, 100 kHz, prototype point of load converter with 36 V input dc source is built to supply power at constant load voltage of either 48 or 28 V. The proposed converters' effectiveness is demonstrated experimentally in terms of reduced source current ripple along with seamless transition from buck to boost mode and vice-versa.

Index Terms— Buck-boost converter, Point of load converter, State-space model, Two-switch buck-boost converter, Voltage-mode controller.

#### I. INTRODUCTION

TITH technological advancements, the requirement of power conversion at high frequencies is soaring and is dominant in applications requiring low power for their operation. Converters for point of load applications are being developed by the designers with special emphasis laid on achieving higher conversion efficiency at full-load, increased power density, and lower radiation. Use of several point of load converters is common in low power dc system wherein many design challenges [1]-[11] must be resolved by the application engineer so as to ensure reliable power distribution. Some of these challenges are: (i) formulation of transformerless non-isolated topologies because minimization or elimination of transformer leakage inductance is a difficult task, (ii) achieving reduced ripples with minimal L, C component requirement, and (iii) reduction

Manuscript received July 17, 2018; revised October 17, 2018; accepted December 18, 2018. Paper 2018-IPCC-0678.R1 presented at 2018 International Power Electronics Conference (IPEC 2018) ECCE ASIA, Niigata, Japan, May. 20 - 24, 2018. (Corresponding author: Mummadi Veerachary)

The authors are with the Department of Electrical Engineering, Indian Institute of Technology Delhi, New Delhi, India (Email: mvchary@ee.iitd.ac.in, eez16494@ee.iitd.ac.in).

in size and weight of the filtering components which results in enhanced power densities. Many dc-dc conversion circuits are present in the literature which produce stable voltages to drive the dc-loads and are briefly classified as: (i) bucking based circuits, (ii) boosting circuits, and (iii) buck-boost and other higher-order or derived converter circuits. These converters find broad application in areas pertaining to controlled power such as: (i) customized low-power integrated circuits, (ii) powering compact and tiny automotive loads, (iii) sophisticated loads such as bio-medical equipment, (iv) internet, wide and local area network services, and (v) telecommunication power supply systems, on-board spacecraft power systems, and defence equipment etc.

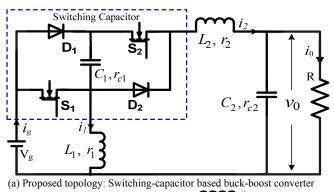

(c) Operation of proposed SBBC in mode-2 Fig. 1. Proposed topology: Switching-capacitor based buck-boost converter.

Fig. 2. Key operational waveforms of the SBBC in Type-A operation.

Recently, Fuel-cell (FC) power systems have become an attractive alternative in providing back-up power in many stand-alone applications [12]. However, they are not stiff voltage sources and thus their output voltages vary over wide ranges (e.g.  $22 \sim 50~V~[12]$ ). Even in automotive vehicle applications, a similar trend in the voltage variation is seen where 12/24~V~dc-supply systems are more popular [13] and the voltage magnitude variation is from 9 to 16 V in the 12 V bus; while it is 18 to 32 V in 24 V bus. In this scenario, the buck-boost topologies provide a viable solution to supply power to loads at constant voltage.

Conventional buck-boost converter (CBBC) is widely used to feed loads which need both voltage bucking as well as boosting [2]-[3]. It has the following salient features: (i) simplicity in structure, (ii) easy converter control due to single switch topology, and (iii) minimum number of energy storage L, C elements thus constituting a second-order system. However, high ripple content and inverted load voltage polarity are the limiting factors of CBBC which affects the input battery life and its reliability. The buck-boost converter with input filter (BBCIF) is able to reduce the source current ripple at the expense of increased system order [4]. However, addition of only the input filter is not recommended because at times it induces unwanted oscillations and may force the system into instability [4]. The insertion of a damping network in the L-C filter helps to stabilize the system by reducing the oscillations. Buck converter cascaded with boost converter (BUBS) or vice-versa i.e. boost converter cascaded with buck converter (BSBU), provides positive load voltage polarity [5]-[6]. However, the selection and design of an appropriate controller becomes essential [7] as these are fourth-order systems and an improper controller may lead to destabilization of the cascaded system.

An attempt to reduce the number of L-C elements in BUBS, from four to two, resulted in a two-switch buck boost

converter (TSBBC) [8]-[9]. This topology has two controlled switches and two diodes, its structure is simple like CBBC and it also offers flexibility in its control. Several studies [10]-[11] pertaining to performance improvement of TSBBC [12]-[14] and its controlling aspects have been reported in the literature. To further enhance the degree of control flexibility. a four-switch buck-boost converter (FSBBC) [15] is evolved by replacing the two diodes with controlled switching devices. This topology offers efficiency improvement against wide variations in the dc-supply voltage but at the cost of increased gate driver requirements associated with four controlled switching devices. TSBBC with an L-C input filter (TSBBF) is reported in [16] to reduce the ripple content on the source side. To overcome some of the limitations of TSBBC, a fourth-order buck-boost converter was reported in [17] where the converter operation was explained in the boost mode. KY converters and their derivatives [18] are popular in realizing the boost based topologies. Using these structures along with additional L-C elements, a fifth-order buck-boost KY converter (FOKYC) was reported in [19]. Although this is a fifth-order topology but it has no right half of s-plane zero (RHPZ) in its control-to-output transfer function and thus it offers improved dynamic performance. Furthermore, FOKYC exhibits lower output voltage ripple due to the presence of L-C filter at the load side. However, the source current ripple is high like in CBBC. Further, it needs a half-bridge driver with a suitable dead-band like in the synchronous buck converter. A new buck-boost converter, restructured form of TSBBC, with low voltage stress has been reported [20]. Though the number of L-C elements and switching devices are identical to TSBBC, but the load ground is isolated from the source ground. Many higher order single switch buck-boost topologies have been presented in the open literature [21]-[22]. Many of these topologies provide the desired voltage gain at low/moderate duty ratios but at the expense of increased system order which in turn restricts the achievable dynamic performance. To combat the limitations prevailing in the aforementioned converters, a switching-capacitor based buck-boost converter (SBBC) is presented in this paper to address the following objectives:

- To achieve smooth source current waveform with low ripple content and that too by using the same number of devices as present in TSBBC;

- (ii) To exhibit low source current ripple irrespective of the mode of operation unlike other converters where this feature is either absent or is present only in a few operating modes;

- (iii) To exhibit minimum-phase behaviour in Type-A operation;

- (iv) To obtain absolute voltage gain same as CBBC with additional feature of common ground;

- (v) To accomplish transition seamlessly from buck to boost mode or vice-versa;

- (vi) To achieve flexibility in the stand-alone operations involving minimal structural changes.

Steady-state analysis, state-space modelling, energy storage element component design, control aspects and performance comparison of SBBC are presented in the upcoming sections.

# II. MODELLING AND ANALYSIS OF SWITCHING-CAPACITOR BASED BUCK-BOOST CONVERTER

A fourth-order switching-capacitor based buck-boost converter is evolved in this paper and shown in Fig. 1. It comprises of a bridge arm containing the active components (switches  $S_1$ ,  $S_2$  with diodes  $D_1$ ,  $D_2$ ) and a capacitor  $C_1$ . It is through this bridge that transfer of energy takes place from source to the load. The two controllable switches of the proposed SBBC provides the following possible control gating schemes: (i) Type-A operation: both switches  $S_1$  and S<sub>2</sub> are in pulse width modulation (PWM) simultaneously, (ii) Type-B operation: S<sub>1</sub> is completely OFF and S<sub>2</sub> is in PWM mode, (iii) Type-C operation: S<sub>1</sub> is in PWM mode and S<sub>2</sub> is continuously in ON-state, (iv) S<sub>1</sub> is continuously in ON-state and  $S_2$  is in PWM mode, and (v)  $S_1$  is in PWM mode  $S_2$  is completely in OFF-state. Amongst these schemes, the first three controlling schemes offer feasible power conversion while the subsequent two needs additional modifications in the circuit to cater reliable power conversion. With the aim to operate SBBC without reconfiguring or introducing additional circuit elements, an attempt is made in this paper to operate the converter using the first three gating control schemes only, as listed in Table-I, so that reliable power conversion is achieved.

### A. Analysis of Switching Capacitor Based Buck-Boost Converter in Type-A Operation

The SBBC topology shown in Fig. 1 performs Type-A operation when its controllable switches S<sub>1</sub> and S<sub>2</sub> undergo PWM mode simultaneously. With this switching action (S<sub>1</sub> and  $S_2$  in PWM together), the capacitor  $C_1$  is connected either at the source side or load side. It is this switching action of the capacitor C<sub>1</sub> which is primarily responsible for the transfer of energy from source to load. When the switches  $(S_1, S_2)$  are ON (mode-1),  $C_1$  gets connected to load side via inductor  $L_2$ , whereas with D<sub>1</sub>, D<sub>2</sub> are ON together (mode-2), C<sub>1</sub> gets connected to the source via inductor L<sub>1</sub>. Due to this interconnection of C<sub>1</sub> with input dc-source in both the modes (either through  $L_1$  or  $L_2$ ), the source current is always equal to the sum of the two inductor currents. As the inductor (L<sub>1</sub> and L<sub>2</sub>) currents are continuous in nature with less ripple content, the dc-source current also exhibits limited ripple content. Although the proposed SBBC has two extra switching devices over CBBC, but it possesses the following salient features: (i) buck-boost features like that of CBBC and conventional TSBBC, (ii) lesser source current ripple for Type-A to Type-C operations, (iii) positive output voltage polarity with common ground between the source and load, and (iv) seamless mode transitions from buck to boost or vice-versa.

## B. Steady-state Performance Analysis of SBBC in Type-A Operation

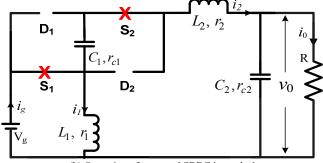

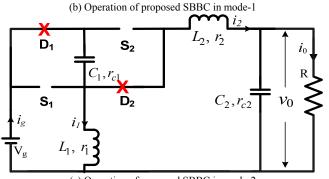

Time-domain analysis of SBBC is established here under the following assumptions: (i) components are ideal, (ii) resistive and energy storage components are linear time-invariant, (iii) all controlled and uncontrolled switching devices are ideal, i.e. zero voltage drop during ON-state, and (iv) switching time-period is very small compared to SBBC circuit time constant. The key waveforms shown in Fig. 2 are useful in obtaining various currents and voltages, voltage gain

and design expressions of energy storage L-C elements. As discussed above, the SBBC operates in Type-A when its two switching devices (S<sub>1</sub>, S<sub>2</sub>) are simultaneously turned-ON/OFF while the diodes (D<sub>1</sub>, D<sub>2</sub>) are simultaneously operating in inverse fashion i.e. turned-OFF/ON. Due to ON-OFF operation of devices (S<sub>1</sub>, S<sub>2</sub>, D<sub>1</sub>, D<sub>2</sub>), the SBBC exhibits two different modes as shown in Fig. 1b and 1c. These equivalent circuits are used to establish KVL/KCL identities, for application of volt-sec/charge-sec balance equations for L-C elements and to finally obtain voltage buck-boost features. In the first mode, energy is stored in  $L_1$ ,  $L_2$  and  $C_1$  while  $C_2$ supplies energy to the load. In the second mode, stored energy is transferred to the load via C1, L2 together with simultaneous charging of capacitor C2. From KVL identities, the voltage across inductive components L<sub>1</sub>, L<sub>2</sub> is obtained as: (i) In mode-1:  $v_{L1} = V_g$ ,  $v_{L2} = (V_g + v_{c1} - v_o)$ ; (ii) In mode-2:  $v_{L1} = (V_g - v_{c1}); v_{L2} = (V_g - v_{c1} - v_0).$  Application of volt-sec balance to the inductor  $L_1$  gives the identity defined by eqn. 1.

$$(D)(V_g) + (1-D)(V_g - v_{c1}) = 0 (1)$$

Simplifying the above equation results in  $v_{c1} = V_g/(1-D)$ , which means that the capacitor  $C_1$  connected at the source side of the SBBC performs the boosting action. Similar approach is extended to the inductor  $L_2$  resulting in eqn. 2.

$$(D)(V_g + v_{c1} - v_o) + (1 - D)(V_g - v_{c1} - v_o) = 0$$

(2)

Incorporating the identity obtained from eqn. 1 together with simplification of eqn. 2 results in the voltage gain expression of SBBC given by eqn. 3. This voltage gain is identical to the gain of CBBC (that too with non-inverted polarity), TSBBC and many other buck-boost converters.

$$M_{Type-A} = \left(\frac{v_0}{V_g}\right) = \frac{D}{(1-D)} \tag{3}$$

For the given input-output specifications, the energy storage elements  $(L_1, L_2, C_1, \text{ and } C_2)$  need to be properly designed so as to meet various ripple standards. From the key waveforms shown in Fig. 2, the ripple currents and voltage expressions can easily be derived using simple time-domain and steady-state analysis along with the network equations. The respective currents of inductor  $L_1$  and  $L_2$  are:

$$i_{1}(t) = \begin{cases} \left(\frac{V_{g}}{L_{1}}\right)t + i_{11}; & \text{for } (k-1)T_{s} < t < (k-1)DT_{s} \\ \left(\frac{V_{g} - v_{c1}}{L_{1}}\right)(t - DT_{s}) + i_{12}; & \text{for } (k-1)DT_{s} < t < kT_{s} \end{cases}$$

$$(4)$$

$$i_{2}(t) = \begin{cases} \frac{\left(V_{g} + v_{c1} - v_{o}\right)}{L_{2}} t + i_{21}; & \text{for } (k-1)T_{s} < t < (k-1)DT_{s} \\ \frac{\left(V_{g} - v_{c1} - v_{o}\right)}{L_{s}} (t - DT_{s}) + i_{22}; & \text{for } (k-1)DT_{s} < t < kT_{s} \end{cases}$$

(5)

From the above two equations, the ripple currents obtained are:

$$\Delta i_1 = DV_g / (L_1 f_s) \tag{6}$$

$$\Delta i_2 = 2DV_g / (L_2 f_s) \tag{7}$$

TABLE -I. FEASIBLE OPERATING CASES OF THE SBBC

| Operation                |       | Type-A     | Туре-В     | Type-C     |  |

|--------------------------|-------|------------|------------|------------|--|

| PWM                      | $S_1$ | PWM        | OFF        | PWM        |  |

| Scheme                   | $S_2$ | PWM        | PWM        | ON         |  |

| Nature of SBBC           |       | Buck-Boost | Buck       | Boost      |  |

| Voltage Gain             |       | D/(1-D)    | D          | 1/(1-D)    |  |

| Nature of Source current |       | Continuous | Continuous | Continuous |  |

| Load voltage polarity    |       | Positive   | Positive   | Positive   |  |

The source current expression  $i_g = (i_1 + i_2)$  is valid equally for both the equivalent circuits given in Figs. 1b and 1c. Accordingly, the average source current is given by

$$I_g = (I_1 + I_2) (8)$$

where  $I_1$ ,  $I_2$  are the average currents flowing through inductors  $L_1$  and  $L_2$  respectively. Inductor  $L_2$  is connected at the load side and its average current is equal to the load current, i.e.  $I_2 = I_0$ . Assuming the power loss within SBBC to be negligible, the power balance in the converter is maintained and is mathematically represented as  $V_g I_g = V_0 I_0$ . Using this power balance identity along with eqn. (3), the average current drawn from source  $V_g$  is obtained as:

$$I_{\sigma} = DI_0 / (1 - D) \tag{9}$$

Solving eqns. (8), (9) along with average inductor current expression of  $L_2$  ( $I_2 = I_0$ ) results in the average current in inductor  $L_1$  and its simplified form is

$$I_1 = (2D - 1)I_0/(1 - D) \tag{10}$$

The peak and valley currents of the inductor  $L_1$  and  $L_2$  are given below which are derived from the known inductor average and ripple current expressions using eqns. (6) to (10).

$$i_{12,11} = \left[ \frac{(2D-1)V_o}{R(1-D)} \pm \frac{DV_g}{(2L_1f_s)} \right]$$

(11)

$$i_{22,21} = \left[ \frac{V_o}{R} \pm \frac{DV_g}{(L_2 f_s)} \right]$$

(12)

From Figs. 1b and 1c, the source current is  $i_g = (i_1 + i_2)$ . Using eqns. (9) to (12), the peak and valley values of the source current obtained are:

$$i_{g(12,11)} = \left\{ \frac{DI_0}{(1-D)} \pm \left( \frac{DV_g}{2f_s} \right) \left[ \frac{1}{L_1} + \frac{2}{L_2} \right] \right\}$$

(13a)

From the above equation the average source current is given by eqn. 9 while its ripple current expression is:

$$\Delta i_g = \left(\frac{DV_g}{f_s}\right) \left[\frac{1}{L_1} + \frac{2}{L_2}\right]$$

(13b)

Eqn. 13b clearly indicates the source ripple current dependency on both the inductors  $(L_1, L_2)$ . From the equivalent circuits shown in Fig. 1b and 1c, the SBBC source current ripple is contributed not only by  $L_1$  but also  $L_2$  and its

relationship is deduced mathematically as given in eqn. 13. This design equation facilitates an easy means to keep the source current ripple within permissible limits. Therefore, the inductors L<sub>1</sub> and L<sub>2</sub> selection is based on the given input/output specifications and permissible source current ripple. Analytically, many combinations of L<sub>1</sub> and L<sub>2</sub> are able to keep  $\Delta i_g$  within permissible limits but according to Eqn. 13b the inductor L<sub>2</sub> ripple content has more impact on source current ripple. Hence, a higher L<sub>2</sub> is recommended. However, larger inductance deteriorates the dynamic response of the SBBC, and therefore to avoid any further deterioration of dynamic response, an upper limit on inductance L<sub>2</sub> must be enforced. Here, the better option is to choose L2 so as to limit its ripple content not exceeding  $20 \sim 40\%$ . Once L<sub>2</sub> selection is finalized, L<sub>1</sub> needs to be suitably chosen such that source current ripples remain within the limits.

The capacitor  $C_1$  carries current  $-i_2$  during mode-1 while  $(i_1 + i_2)$  flows through it in mode-2 operation. From eqns. (11) and (12), the capacitor  $C_1$  ripple current is

$$\Delta i_{C1} = (i_{12} + 2i_{22}) = \left\{ \frac{I_0}{(1 - D)} + \left( \frac{DV_g}{2f_s} \right) \left[ \frac{1}{L_1} + \frac{4}{L_2} \right] \right\}$$

(14)

From mode-1 and 2 equivalent circuits,

$$i_2 = (I_{2_a \text{reg}} + \Delta i_{L2}) = (I_0 + \Delta i_{C2})$$

(15)

Eqn. (15) indicates that the average current of inductor  $L_2$  flows through the load while its ripple current flows through the capacitor  $C_2$ . Therefore, the capacitor  $C_2$  ripple current is

$$\Delta i_{C2} = \Delta i_{L2} = 2DV_g / (L_2 f_s) \tag{16}$$

Eqns. (14) and (16) are used to compute the ripple voltages and they are:

$$\Delta v_{C_1} = \left(\Delta i_{C_1} D / (C_1 f_s)\right) \tag{17}$$

$$\Delta v_{C2} = \left(\Delta i_{C2} D / (C_2 f_s)\right) \tag{18}$$

Using the ripple current and voltage expressions (6, 7, 17 and 18) established above, SBBC component design expressions are formulated and given in Table-III.

#### C. Small-signal models of SBBC

Fig. 1b and 1c represents the equivalent circuits of SBBC in one switching cycle. The process of energy storage and release is discussed in Section II-B. As SBBC behaviour is essentially determined by the inductor currents and capacitor voltages, the resulting network formulations must be defined in terms of currents and voltages of the energy storage elements. Through network analysis of SBBC, a set of first-order differential equations in terms of capacitor voltages and inductor currents are formulated and transformed into compact form using matrix notation as stated in eqn. 19.

$$\begin{bmatrix} \dot{x} \end{bmatrix} = \begin{bmatrix} A_k \end{bmatrix} \begin{bmatrix} x \end{bmatrix} + \begin{bmatrix} B_k \end{bmatrix} \begin{bmatrix} u \end{bmatrix}

\begin{bmatrix} y \end{bmatrix} = \begin{bmatrix} E_k \end{bmatrix} \begin{bmatrix} x \end{bmatrix} + \begin{bmatrix} F_k \end{bmatrix} \begin{bmatrix} u \end{bmatrix}$$

$$t_k < t < t_{(k+1)}$$

(19)

here  $[A_k]$  is the system state matrix,  $[B_k]$  the input matrix,  $[E_k]$  the output matrix, [x] the state vector, [y] the output vector, and [u] is the input forcing function vector. The small-signal

transfer functions, both in s and z-domain, can easily be obtained from eqn. 19 after its linearization [23]. The state-space model matrices for Type-A Operation are:

$$[A_{1}] = \begin{bmatrix} \frac{-r_{1}}{L_{1}} & 0 & 0 & 0\\ 0 & \frac{-k_{12}}{L_{2}} & \frac{1}{L_{2}} & \frac{-k_{13}}{L_{2}}\\ 0 & \frac{-1}{C_{1}} & 0 & 0\\ 0 & \frac{k_{13}}{C_{2}} & 0 & \frac{-k_{13}}{RC_{2}} \end{bmatrix}; [A_{2}] = \begin{bmatrix} \frac{-k_{14}}{L_{1}} & \frac{-r_{c1}}{L_{1}} & \frac{-1}{L_{1}} & 0\\ \frac{-r_{c1}}{L_{2}} & \frac{-k_{12}}{L_{2}} & \frac{-1}{L_{2}} & \frac{-k_{13}}{L_{2}}\\ \frac{1}{C_{1}} & \frac{1}{C_{1}} & 0 & 0\\ 0 & \frac{k_{13}}{C_{2}} & 0 & \frac{-k_{13}}{RC_{2}} \end{bmatrix}; (20a)$$

$$B_{1} = B_{2} = \begin{bmatrix} 1/L_{1} & 1/L_{2} & 0 & 0 \end{bmatrix}^{T}; \begin{bmatrix} E_{1} \end{bmatrix} = \begin{bmatrix} E_{2} \end{bmatrix} = \begin{bmatrix} 0 & k_{11} & 0 & k_{13} \end{bmatrix}; (20b)$$

$$k_{11} = Rr_{c2}/(R + r_{c2}); k_{12} = (r_{2} + r_{c1} + k_{11}); k_{13} = (k_{11}/R); k_{14} = (r_{1} + r_{c1});$$

These state-space model matrices are used to generate the transfer functions and the relevant discussion is given in Section III.

#### D. Analysis of SBBC in Type-B and Type-C Operation

Detailed analysis of Type-A operation was explained in the above section. Following the same methodology, analysis of Type-B and Type-C operation is established and briefly explained here. In Type-B operation of SBBC, S<sub>1</sub> is completely OFF and S<sub>2</sub> is in PWM mode, while in Type-C operation the switch  $S_1$  is in PWM mode and  $S_2$  is continuously in the ON-state. Therefore, the SBBC equivalent circuits in Type-B or Type-C operation will also be different. In each of these operations, SBBC exhibits two different equivalent circuits and the corresponding inductor voltage expressions are tabulated in Table IV for ready use. The application of volt-sec balance to these inductor voltages followed by their simplification results in the corresponding voltage gains as listed in the same table. The state-space model matrices for Type-B and Type-C operations are also given by eqns. (21) and (22).

State-space model matrices for Type-B operation:

$$[A_{1}] = \begin{bmatrix} \frac{-k_{14}}{L_{1}} & 0 & \frac{-1}{L_{1}} & 0\\ 0 & \frac{-k_{15}}{L_{2}} & 0 & \frac{-k_{13}}{L_{2}}\\ \frac{1}{C_{1}} & 0 & 0 & 0\\ 0 & \frac{k_{13}}{C_{2}} & 0 & \frac{-k_{13}}{RC_{2}} \end{bmatrix}; [A_{2}] = \begin{bmatrix} \frac{-k_{14}}{L_{1}} & \frac{-r_{c1}}{L_{1}} & \frac{-1}{L_{1}} & 0\\ \frac{-r_{c1}}{L_{2}} & \frac{-k_{12}}{L_{2}} & \frac{-1}{L_{2}} & \frac{-k_{13}}{L_{2}}\\ \frac{1}{C_{1}} & \frac{1}{C_{1}} & 0 & 0\\ 0 & \frac{k_{13}}{C_{2}} & 0 & \frac{-k_{13}}{RC_{2}} \end{bmatrix};$$

(21a)

$[B_1] = [B_2] = [1/L_1 \quad 1/L_2 \quad 0 \quad 0]^T; [E_1] = [E_2] = [0 \quad k_{11} \quad 0 \quad k_{13}]; (21b)$ State-space model matrices for Type-C operation:

$$[A_{1}] = \begin{bmatrix} \frac{-r_{1}}{L_{1}} & 0 & 0 & 0\\ 0 & \frac{-k_{12}}{L_{2}} & \frac{1}{L_{2}} & \frac{-k_{13}}{L_{2}}\\ 0 & \frac{-1}{C_{1}} & 0 & 0\\ 0 & \frac{k_{13}}{C_{2}} & 0 & \frac{-k_{13}}{RC_{2}} \end{bmatrix}; [A_{2}] = \begin{bmatrix} \frac{-k_{14}}{L_{1}} & 0 & \frac{-1}{L_{1}} & 0\\ 0 & \frac{-k_{15}}{L_{2}} & 0 & \frac{-k_{13}}{L_{2}}\\ \frac{1}{C_{1}} & 0 & 0 & 0\\ 0 & \frac{k_{13}}{C_{2}} & 0 & \frac{-k_{13}}{RC_{2}} \end{bmatrix}; (22a)$$

$$[B_1] = [B_2] = [1/L_1 \quad 1/L_2 \quad 0 \quad 0]^T; [E_1] = [E_2] = [0 \quad k_{11} \quad 0 \quad k_{13}]; (22b)$$

E. Performance Comparison of SBBC with other Buck-Boost Topologies

Here, SBBC performance is compared with other buckboost converter topologies. In the proposed SBBC the two inductors L<sub>1</sub> and L<sub>2</sub> contribute towards the source current  $(i_{g SBBC}=i_{LI}+i_{L2})$  while in conventional CUK converter [2], the source current is contributed by only inductance L<sub>1</sub>  $(i_{g CUK}=i_{L1})$ . With identical inductances and input/output voltages, the source current ripple is somewhat higher in the SBBC. However in SBBC and CUK converters, the ripple current in the load side capacitor C2 is more or less same and is low on account of the second inductance L2. Though the CUK converter exhibits little lower source ripple content over SBBC but it has many other limitations highlighted in Table II-A. Moreover, it is not feasible for multi-mode operation. For the identical input inductance L<sub>1</sub>, input and output voltages, SBBC standalone operation in boost mode (Type-C operation) is compared with the conventional boost converter operation. The source current ripple in SBBC under Type-C operation is slightly higher over the conventional boost converter due to ripple current of inductance L<sub>2</sub> but the presence of inductance L2 in SBBC and its operation in boost mode (Type-C mode) has a positive impact in terms of substantial reduction in the load side capacitor C2 ripple current. In the conventional boost converter there is no second inductance L<sub>2</sub> and thus the pulsating diode ripple current flows through the load side capacitor. Therefore, SBBC operation in boost mode (Type-C operation) results in reduced capacitor stress over the conventional boost converter. After extensive analysis of various topologies listed in references, a comparison of SBBC performance parameters with other buck-boost topologies is listed in Table-II.

Figs. 1b and 1c indicate the energy transfer phenomena in the proposed SBBC wherein the dc source remains connected to load via L/C elements in both the operating modes. While in most of the buck-boost topologies, (CBBC, CUK, SEPIC etc.,), the source may not have a connection through L/C elements to the load in any of the operating modes. In many of these topologies, the energy is first stored in the L/C elements and later it is transferred to load and thus there is a finite timedelay in energy transfer from source to load. For example, in CUK converter [2], when the switch turns-ON, the energy is first stored in the inductance L<sub>1</sub> and is then transferred to capacitor C<sub>1</sub> in the subsequent switch turn-OFF duration. Thus, the load receives power from source through an indirect energy transfer and this delay impact is reflected through a right half of s-plane zero(s) (RHPZ) in the control-to-output transfer function (COTF). But in SBBC, direct energy transfer takes place from source to load on continuous basis irrespective of the switching operations, indicated in the equivalent circuits Figs. 1b and 1c, and this hidden fact can easily be understood by examining the COTF given in Section III. From multi-mode perspective all the topologies listed in Table II-B (TSBB, TSBBF, BUBS and SBBC) uses identical number of devices. But from the smooth current waveforms

point of view, SBBC is better option than other topologies. Furthermore, SBBC belongs to a class of minimum-phase systems as its COTF has no RHP zeros and hence exhibits better dynamic performance.

#### F. SBBC L-C Component Design

The expressions given in eqns. 6 and 7 clearly indicate that the ripple content of L<sub>1</sub>/L<sub>2</sub> is directly proportional to duty ratio. Current ripple is higher in boosting operation and thus higher inductances L<sub>1</sub>/L<sub>2</sub> are needed to meet the specified ripple content. However, high inductance leads to inferior dynamic performance and thus it is difficult to meet transient performance specifications. In this paper, considering the buck operation as the basis, the design is initiated ( $\Delta i_{Ll} \le 50\%$ ,  $\Delta i_{L2} \leq 30\%$ ,  $\Delta v_C \leq 5\%$ ) and the trade-off values are arrived at after enforcing the source current ripples ( $\Delta i_e$ =1.0 A). Using eqns. 6 to 13 with  $V_g=36 \text{ V}$  and  $f_s=100 \text{ kHz}$ , the inductances are computed as: (a) bucking case:  $V_0=28$  V, R=15  $\Omega$ , D=0.44,  $\Delta i_{Ll}$ =0.2 A, L<sub>1</sub> $\geq$  792  $\mu$ H,  $\Delta i_{L2}$ =0.374 A, L<sub>2</sub> $\geq$  847  $\mu$ H,  $\Delta i_{\sigma}$ =0.6 A; (b) boosting case:  $V_{o}$ =48 V, R=70  $\Omega$ , D=0.6,  $\Delta i_{LI}$ =0.18 A, L<sub>1</sub> $\geq$  1200  $\mu$ H,  $\Delta i_{L2}$ =0.14 A, L<sub>2</sub> $\geq$  3100  $\mu$ H,  $\Delta i_g$ =0.32 A. The boosting case design (L<sub>1</sub> $\geq$  1200  $\mu$ H, L<sub>2</sub> $\geq$ 3100 µH) yields low ripples but the corresponding inductances are on higher side. A trade-off design is obtained after making a compromise in  $\Delta i_g$  (<1.0 A) and the final chosen inductances are:  $L_1=800 \mu H$ ,  $L_2=1000 \mu H$ . Using these inductance values, ripple voltage constraint along with eqns. 17 and 18 the capacitances  $C_1$  and  $C_2$  are computed.

TABLE -III. SBBC PARAMETER DESIGN EXPRESSIONS

| Parameter | Expression                          |

|-----------|-------------------------------------|

| $L_1 \ge$ | $DV_g/(f_s\Delta i_1)$              |

| $L_2 \ge$ | $2DV_g/(f_s\Delta i_2)$             |

| $C_1 \ge$ | $\Delta i_{C1}D/(f_s\Delta v_{C1})$ |

| $C_2 \ge$ | $\Delta i_{C2}D/(f_s\Delta v_{C2})$ |

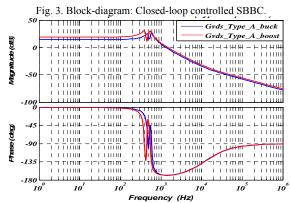

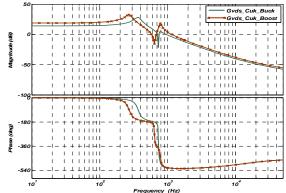

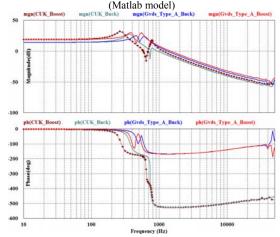

(a) Frequency response of control-to-output transfer functions (Matlab model)

(b) Frequency response of CUK converter control-to-output transfer functions

(c) Frequency response of control-to-output transfer functions (SBBC and CUK, generated from PSIM simulator [26] for model verification)

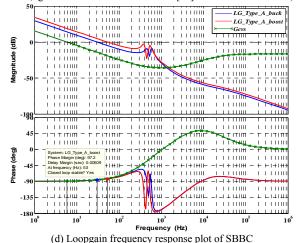

Fig. 4. Frequency response plots.

TABLE -IV. INDUCTOR VOLTAGES: TYPE-B/TYPE-C OPERATION

| Quantity            | Туре-В           | Operation              | Type-C Operation       |                  |  |  |

|---------------------|------------------|------------------------|------------------------|------------------|--|--|

|                     | Mode-1           | Mode-2                 | Mode-1                 | Mode-2           |  |  |

| $v_{L1}$            | $(V_g - v_{c1})$ | $(V_g - v_{c1})$       | $V_g$                  | $(V_g - v_{c1})$ |  |  |

| $v_{L2}$            | $(V_g - v_0)$    | $(V_g - v_{c1} - v_o)$ | $(V_g + v_{c1} - v_o)$ | $(V_g - v_o)$    |  |  |

| Voltage<br>gain (M) | $M_{T_2}$        | $_{pe-B}=D$            | $M_{Type-C} = 1/(1-D)$ |                  |  |  |

#### III. CLOSED-LOOP CONTROLLER DESIGN

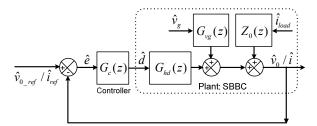

The linear control system theory is well established and is applied in many real-time control system designs [24]. It adopts the frequency domain models for controller design and to characterize both the absolute and relative stability aspects of closed-loop controlled system. The block-diagram representation of SBBC along with single-loop voltagemode/current-mode controller is shown in Fig. 3. Here, the plant transfer functions are:  $G_{hd}(z)$ ,  $G_{vo}(z)$ ,  $Z_0(z)$ , and they are dependent on type of operation of SBBC (Type-A, Type-B and Type-C). From the known state-space model (eqn. 19) matrices, formulated for Type-A, Type-B and Type-C operations in Section II, these plant transfer functions can easily be obtained [20]. Here, the controller transfer function G<sub>c</sub>(z) is in the feed-forward path along with the control-tooutput transfer function  $G_{hd}(z)$  (where  $G_{hd}(z)$  is  $G_{vd}(z)$  for voltage control and G<sub>id</sub>(z) for current control). As it is inferred that the SBBC plant transfer functions are dependent on the type of operation (Type-A, Type-B and Type-C), it is difficult to stabilize the converter using solely one unique controller. Even if the unique controller  $G_c(z)$  is able to stabilize Type-A, Type-B and Type-C operation of SBBC, the achievable relative stability limits are going to be different and thus will lead to differences in the disturbance rejection capability. Furthermore, Type-C operation/boost mode presents nonminimum phase (NMP) [24] behaviour and thus the corresponding G<sub>c</sub>(z) has to have a low bandwidth. On the other hand, the Type-B operation/buck-mode yields minimum phase [24] behaviour and thus the corresponding controller G<sub>c</sub>(z) can have higher bandwidths leading to better dynamic response of the closed-loop system.

The above discussion envisages that change of SBBC operation, from Type-B to Type-C or vice-versa, must be accompanied by respective change in its controller (high to low bandwidth or vice-versa). In Type-A PWM gating scheme, the direct duty ratio control is a straight forward technique to change the SBBC operation from buck to boost or vice versa without involvement of any controller changeover mechanism. A single controller with a trade-off in bandwidth is sufficient enough to perform voltage/current regulation. In view of this, a single-loop digital voltagemode/current-mode controller is designed in the paper using the approach mentioned in [23] to achieve the desired load voltage/current regulation. For the controller design, singleinput single output tool of Matlab [25] is used and poles and zeros are placed at the desired locations such that the resulting closed-loop system exhibits absolute stability. Once it satisfies the absolute stability criterion, it becomes necessary to choose a controller which ensures the relative stability specifications. To ensure that the closed-loop SBBC performs load voltage/current regulation both in the buck and boost mode against perturbations either in the line or load side, the crossover frequency is kept at lower side so that the loopgain frequency response has an adequate gain margin (GM) (> 6 dB or higher).

The controller design is initiated using the following SBBC parameters:  $L_1$ =800  $\mu$ H,  $L_2$ =1000  $\mu$ H,  $C_1$ =47  $\mu$ F,  $C_2$ =100  $\mu$ F. Using eqns. 19 to 22, the plant transfer functions indicated in Fig. 3 are computed. The control-to-output

voltage and control-to-inductor current transfer functions for D=0.44, D=0.57 are given in eqns. 23 and 24.

$$G_{vd}(s) = \frac{[a_{4v}s^4 + a_{3v}s^3 + a_{2v}s^2 + a_{1v}s + a_{0v}]}{[b_{4v}s^4 + b_{3v}s^3 + b_{2v}s^2 + b_{1v}s + b_{0v}]}$$

(23)

$$G_{id}(s) = \frac{\left[a_{4i}s^4 + a_{3i}s^3 + a_{2i}s^2 + a_{1i}s + a_{0i}\right]}{\left[b_{4i}s^4 + b_{3i}s^3 + b_{2i}s^2 + b_{1i}s + b_{0i}\right]}$$

(24)

where the constant coefficients are: (i) D=0.44:  $a_{4\nu}$ =0,  $a_{3\nu}$ =782.2,  $a_{2\nu}$ =5.812xe<sup>7</sup>,  $a_{I\nu}$ =2.155xe<sup>10</sup>,  $a_{0\nu}$ =6.168xe<sup>14</sup>,  $b_{4\nu}$ =1,  $b_{3\nu}$ =881.7,  $b_{2\nu}$ =2.264Xe<sup>7</sup>,  $b_{I\nu}$ =9.946xe<sup>9</sup>,  $b_{0\nu}$ =1.202xe<sup>14</sup>,  $a_{4i}$ =0,  $a_{3i}$ =1.279xe<sup>5</sup>,  $a_{2i}$ =6.105xe<sup>7</sup>,  $a_{Ii}$ =1.369xe<sup>12</sup>,  $a_{0i}$ =3.393xe<sup>14</sup>,  $b_{4i}$ =1,  $b_{3i}$ =881.7,  $b_{2i}$ =2.264Xe<sup>7</sup>,  $b_{Ii}$ =9.946xe<sup>9</sup>,  $b_{0i}$ =1.202xe<sup>14</sup>, (ii) D=0.57:  $a_{4\nu}$ =0,  $a_{3\nu}$ =1027,  $a_{2\nu}$ =7.63xe<sup>7</sup>,  $a_{I\nu}$ =1.894xe<sup>10</sup>,  $a_{0\nu}$ =6.162xe<sup>14</sup>,  $b_{4\nu}$ =1,  $b_{3\nu}$ =753.7,  $b_{2\nu}$ =1.771xe<sup>7</sup>,  $b_{I\nu}$ =6.38xe<sup>9</sup>,  $b_{0\nu}$ =6.975xe<sup>13</sup>,  $a_{4i}$ =0,  $a_{3i}$ =1.677xe<sup>5</sup>,  $a_{2i}$ =4.732xe<sup>7</sup>,  $a_{Ii}$ =1.362xe<sup>12</sup>,  $a_{0i}$ =1.937xe<sup>14</sup>,  $b_{4i}$ =1,  $b_{3i}$ =753.7,  $b_{2i}$ =1.771xe<sup>7</sup>,  $b_{Ii}$ =6.38xe<sup>9</sup>,  $b_{0i}$ =6.975xe<sup>13</sup>. The controller transfer function in discrete-time domain is

$$G_{cv}(z) = \frac{k_{1v}(z + a_{1v})(z + a_{2v})}{(z + b_{1v})(z + b_{2v})}$$

(25a)

$$G_{ci}(z) = \frac{k_{1i}(z + a_{1i})(z + a_{2i})}{(z + b_{1i})(z + b_{2i})}$$

(25b)

where  $k_{Iv}$ =0.15,  $a_{Iv}$ =-0.9614,  $a_{2v}$ =-0.949,  $b_{Iv}$ =-1.0,  $b_{2v}$ =-0.1984,  $k_{Ii}$ =0.38095,  $a_{Ii}$ =-0.9806,  $a_{2i}$ =-0.9849,  $b_{Ii}$ =-1.0,  $b_{2i}$ =-0.5019 parameters will keep the voltage/current control loop stable. For identical parameters, the frequency response of COTF of SBBC and CUK converters is plotted in Fig. 4a to 4c. In case of SBBC, the COTF has four left half of s-plane (LHP) poles (two complex conjugate pairs) and three LHP zeros (one real and one complex conjugate pair). While the CUK converter COTF has four LHP poles (two complex conjugate pairs) and three zeros (one real LHP zero and one complex conjugate RHP zero pair). The magnitude plot trend of SBBC and CUK converters is almost similar whereas a considerable deviation is seen in the CUK converter phase plot. In SBBC, the phase starts from 0° and rolls-off close to 180° at the resonating frequency and due to LHP zeros it finally settles to 90° in the high frequency region. On the other-hand, CUK converter phase start from 0° and with increase in frequency it rolls down close to 540° due to RHP zeros and then finally settles at 450°. These frequency responses generated in MATLAB using the mathematical models, eqns. 19 to 22, are now validated through frequency responses obtained from PSIM circuit-simulator [26] as shown in Fig. 4c. It is seen that the model based frequency responses are in close agreement with the frequency responses obtained from the PSIM simulator. Frequency response plots of loopgain transfer functions (SBBC buck and boost operations) is given in Fig. 4d. These frequency responses clearly show the stability of the closed-loop controlled system of SBBC both in bucking and boosting mode.

#### IV. EXPERIMENTAL RESULTS

The validity of the analytical findings of the proposed buck-boost converter established in the preceding sections is now demonstrated through experimental measurements [27]. For experimentation, a  $30 \sim 55$  W, 100 kHz prototype

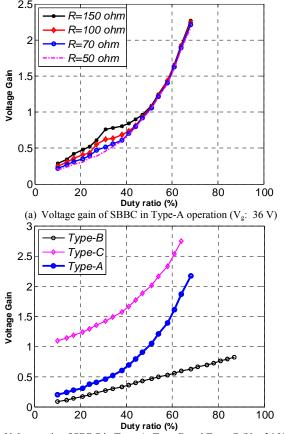

converter circuit was built using the L-C components and they are:  $L_1$ = 800  $\mu$ H,  $L_2$ =1000  $\mu$ H,  $C_1$ =33  $\mu$ F,  $C_2$ =100  $\mu$ F. nominal voltage of 36 V is used as a dc source. The SBBC's performance both in bucking as well as in boosting mode is verified by fixing the reference load voltage to 28 V (~20%) below the nominal  $V_g$ ,  $P_o$ : ~53 W) in bucking mode and 48 V ( $\sim$ 20% above the nominal  $V_g$ ,  $P_o$ : 34 W) in boosting mode. Keeping the nominal source voltage as 36 V, the voltage gain of the SBBC is measured by varying the duty-ratio and is plotted in Fig. 5a for different loads (R=150, 100, 70 and 50  $\Omega$ ). It is seen that the voltage gain increases with increase in the duty-ratio. Further, for duty-ratios less than 50%, the voltage gain remains less than one which implies bucking action of SBBC in Type-A operation. However, a slight variation in the gain of SBBC is observed at different loads, which is due to the loading effect. At higher loads (R=50  $\Omega$ ) the parasitic voltage drops are dominant, like in other dc-dc converter systems, leading to a slight fall in the voltage gain.

(b) Voltage gain of SBBC in Type-A, Type-B and Type-C ( $V_g$ : 36 V) Fig. 5. Measured voltage gain variation with duty ratio.

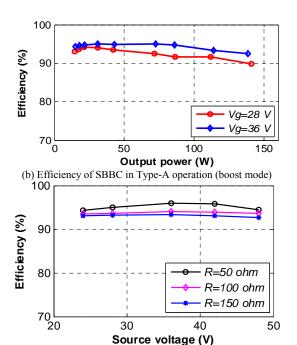

(c) SBBC efficiency variation with input supply voltage (Type-A operation)

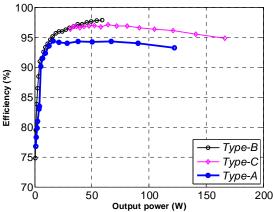

(d) Efficiency of SBBC in Type-A, Type-B and Type-C operations Fig. 6. Measured SBBC efficiency variation with power output and supply voltage.

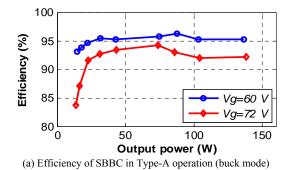

The SBBC mode changeover from buck to boost takes place close to 50% of duty ratio for all the loads as seen in Fig. 5a. For the duty ratios above 50%, the gain of SBBC is rising indicating its boosting behavior. A similar trend is seen for all loading conditions mentioned above but the impact of the loading on the voltage gain is negligible, unlike in the bucking mode. Further, the SBBC voltage gain is also measured for the Type-B and C operations and is compared with the Type-A operation as shown in Fig. 5b. The measured voltage gain plots obtained closely resemble the conventional buck and boosting operations. This substantiates the flexibility of SBBC, which supports all three operations (buck-boost, buck and boost) without the use of additional circuit elements and exhibits seamless transitions. The variation of efficiency with power output for all the three operating modes is shown in Fig. 6. Here, the efficiency of SBBC in Type-A operation is measured for two different cases, which are: (a) Fig. 6a- Buck mode:  $V_g=60$ , 72 V,  $V_o=48$  V, (b) Fig. 6b- Boost mode:  $V_g=28$ , 36 V,  $V_o=48$  V. In both these test conditions, the

SBBC exhibited efficiency close to 95%. However, a slight fall in efficiency is observed in the cases (( $V_g$ =72 V,  $V_o$ =48 V), ( $V_g$ =28 V,  $V_o$ =48 V)) where SBBC involves more bucking/boosting. The efficiency plot for variation in the input voltage is shown in Fig. 6c. It is seen that the SBBC exhibits higher efficiencies at higher loading conditions and it is slightly less efficient at lighter loads. The fall in the efficiency in the latter case is because of more losses. The SBBC efficiency variation with power output for Type-A, B and C operation is shown in Fig. 6d. Here, Type-B/Type-C operations exhibit a little higher efficiency compared to Type-A operation because the former case uses only three switching devices whereas the latter uses all the four devices together.

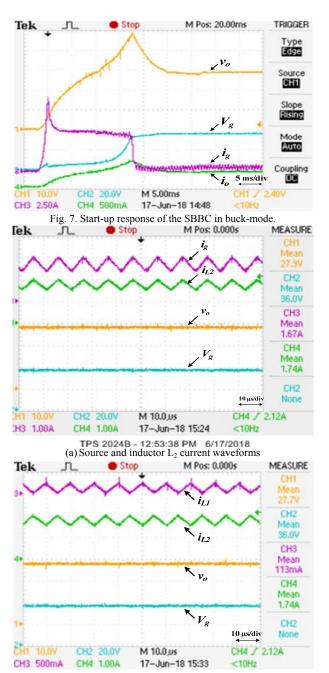

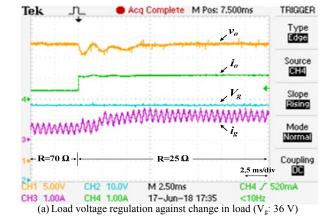

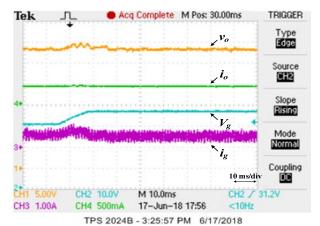

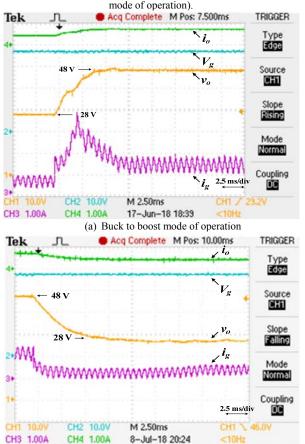

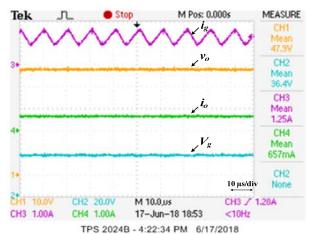

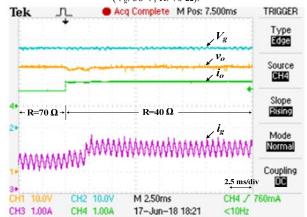

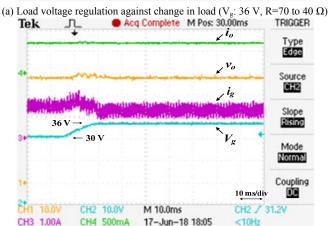

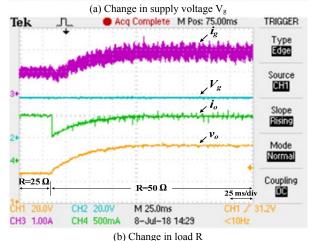

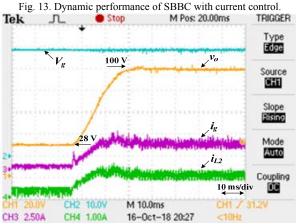

A controller (eqn. 25a) is designed to regulate the SBBC load voltage and to ensure closed-loop system stability against line and load variations. To begin with, SBBC load voltage reference is set to 28 V with a 70  $\Omega$  load and the start-up performance under closed-loop control is measured and is shown in Fig. 7. The steady-state waveforms of SBBC in the bucking case with V<sub>o ref</sub>=28 V are shown in Fig. 8. As seen in the figure, the inductor L<sub>1</sub> and L<sub>2</sub> currents are continuous while the source current is smooth and has low ripple content  $(\Delta i_g \sim 0.5 \text{ A})$ . After performing rigorous characterization of SBBC under dynamic conditions, a few measurement results with illustrations are presented in Figs. 9 to 13. Firstly, the dynamic performance of SBBC in the bucking mode is given for the following test conditions: (a) load voltage regulation against change in (R) load from 70 to 25  $\Omega$  (V<sub>g</sub>: 36 V), and (b) load voltage regulation against variation in source (Vg) from 30 to 36 V (R: 70  $\Omega$ ). These dynamic tests (Fig. 9) indicate that the load voltage regulation is achieved in 7.5 ms against load variations while it takes a little longer to achieve regulated output voltage (~15 ms) against source voltage variation. Faster dynamic response of SBBC is seen in case of load variation compared to source variation. Next, to see the effectiveness of SBBC during mode transition, reference voltage is changed from 28 to 48 V and the corresponding dynamic performance measurement is shown in Fig. 10. As seen, the transition is seamless for load voltage change from 28 to 48 V and vice-versa. Furthermore, the time taken to make this transition is close to 5.0 ms. The steady-state performance of SBBC measured in boost mode is shown in Fig. 11. In this mode also the source current is smooth with low ripple content. The dynamic performance of SBBC in boost mode (Fig. 12) is alike buck mode with the following operating conditions: (a) load voltage regulation against change in (R) load from 70 to 40  $\Omega$  (V  $_{\!g}\!\!:$  36 V), and (b) load voltage regulation against variation in source (Vg) from 30 to 36 V (R: 70  $\Omega$ ). In the first case, the load voltage regulation is achieved within 3.0 ms while it takes close to 10.0 ms under source perturbations.

(b) Load voltage and inductor  $L_1$ ,  $L_2$  current waveforms Fig. 8. Steady-state waveforms of the SBBC under buck mode of operation  $(V_g: 36\ V)$ .

(b)Load voltage regulation against change in source voltage (Vg. 30 to 36 V, R=70  $\Omega$ )

Fig. 9. Dynamic performance of SBBC against line and load variations (buck

(b) Boost to buck mode of operation Fig. 10. Dynamic performance of SBBC under mode-transition ( $V_g$ : 36 V, R: 70  $\Omega$ ).

TPS 2024B - 5:55:14 PM 7/8/2018

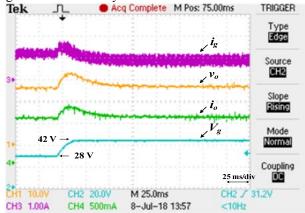

The proposed SBBC's performance is also demonstrated at even higher voltage and power levels. The measured result shown in Fig. 14 (for  $V_g$ : 48 V, R: 100  $\Omega$ ,  $V_{o\_ref}$ : 28 to 100 V) shows its performance both in bucking as well as boosting mode. The proposed SBBC performs not only voltage regulation but also current regulation effectively. To demonstrate this, a digital current-mode controller, eqn. 25b, is designed to regulate the load current. The current-loop is designed to regulate a current of 1.0 A at a nominal source voltage of 36 V as shown in Fig. 13a and 13b. The

effectiveness of current regulation is shown in Fig. 13 for variation in (i) supply voltage (28 to 42 V), (ii) load (25 to 50  $\Omega$ ) and (iii) reference current (1.0 to 1.5 A). In all these cases current regulation is achieved effectively. This exhaustive experimental study reveals that SBBC is (i) maintaining low ripple content in the source current irrespective of its operating modes, (ii) successful in achieving load voltage/current regulation against line and load variations, and (iii) undergoing seamless mode transition.

Fig. 11. Steady-state waveforms of SBBC under boost mode of operation ( $V_g$ : 36 V, R: 70  $\Omega$ ).

(b) Load voltage regulation against change in source voltage (Vg. 30 to 36 V, R=70  $\Omega$ )

Fig. 12. Dynamic performance of SBBC against line and load variations (boost mode of operation).

CH3 1.00A

#### V. CONCLUSION

switching-capacitor based buck-boost exhibiting identical voltage gain as that of conventional Buckboost/Two-switch buck-boost converter was proposed. Detailed analysis revealed that the proposed converter uses the degree of freedom offered by the PWM gating scheme and is able to operate in three different modes (Type-A: buckboost, Type-B: buck, and Type-C: boost) with minimal structural modifications. Detailed analysis was established and voltage-mode/current-mode single-loop controller, controller, was designed. The effectiveness of SBBC in closed-loop operation was demonstrated experimentally both for bucking as well as boosting operations. It exhibited low source current ripple content irrespective of its mode of operation (buck-boost, buck, and boost). Furthermore, Type-A operation exhibited seamless transition from buck to boost mode and vice-versa successfully. The measured results are congruent with the analytical studies.

Acq Complete M Pos: 75.00ms TRIGGER Tek Туре Edge vo Source CH4 Rising Mode 1.5 A Normal  $V_g$ Coupling 25 ms/div CH4 / CH2 20.0V M 25.0ms

8-Jul-18 18:05 (c) Change in current reference (I<sub>0</sub>=1.0 to 1.5 A)

<10Hz

CH4 500mA

Fig. 14. Dynamic performance of SBBC at higher power level  $(V_g: 48 \text{ V}, \text{ R}: 100 \Omega, V_{0-\text{ref}}: 28 \text{ to } 100 \text{ V}).$

### REFERENCES

- G.W. Wester and R.D. Middlebrook, "Low-frequency characterization of switched DC-DC converters," in Proc. of IEEE Power Electronics Specialists Conference, pp. 9-20, 1972.

- S. Cuk, "General topological properties of switching structures," in Proc. Of IEEE Power Electronics Specialists Conference, pp. 109–130,

- D. Maksimovic and S. Cuk, "Switching converters with wide DC conversion range," IEEE Trans. Power Electron., vol. 6, no. 1, pp. 151-157, Jan. 1991

- [4] K. Louati, D. Sadarnac, and C. Karimi, "Input filter influence on the control stability of DC/DC converters," in Proc. IEEE Int. Symp. Ind. Electron., vol. 2, pp. 1165-1171, 2004.

- Jingquan Chen, Dragan Maksimovic, Robert W. Erickson, "Buck-boost PWM converters having two independently controlled switches," Proc. of IEEE Power Electronics Specialists Conference, vol. 2, pp. 736-741,

- X. Ren, X. Ruan, H. Qian, M. Li and Q. Chen, "Three-mode dualfrequency two-edge modulation scheme for four-switch buck-boost converter," IEEE Trans. Power Electron., vol. 24, no. 2, pp. 499-509, Feb. 2009.

- X. G. Feng, J. J. Liu and F. C. Lee, "Impedance specifications for stable de distributed power systems," IEEE Trans. Power Electron., vol. 17, no. 2, pp. 157-162, Mar. 2002.

- Y. J. Lee, A. Khaligh and A. Emadi, "A compensation technique for smooth transitions in non-inverting buck-boost converter," Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition, pp. 608-614, 2009.

- R. Dowlatabadi, M. Monfared, S. Golestan and A. Hassanzadeh, "Modelling and controller design for a non-inverting buck-boost chopper," in Proc. IEEE International Conference on Electrical Engineering and Informatics, pp. 1-4, 2011.

- [10] C. Yao, X. Ruan, W. Cao and P. Chen, "A two-mode control scheme with input voltage feed-forward for the two-switch buck-boost DC-DC

- converter," IEEE Trans. Power Electron., vol. 29, no. 4, pp. 2037–2048, April 2014.

- [11] C. Yang, S. Xie, L. Mao, and Z. Zhang, "Efficiency improvement on two-switch buck-boost converter with coupled inductor for high-voltage applications," *IET Power Electron.*, vol. 7, no. 11, pp. 2846–2856, 2014.

- [12] H.K. Liao, T.J. Liang, L.S. Yang, J.F. Chen, "Non-inverting buck-boost converter with interleaved technique for fuel-cell system," *IET Power Electron.*, vol. 5, no. 8, pp. 1379–1388, Sep. 2012.

- [13] M. Alexander, "Automotive LED lighting needs special drivers," Power Electron. Technol., pp. 22–28, 2005.

- [14] K. J. Pai, "Depressing start-up current overshoot for a laser headlight driver in high-temperature and forward voltage drift conditions," *IEEE Trans. Ind. Electron.*, vol. 65, no. 10, pp. 7793–7804, Oct. 2018.

- [15] Y. Qin, S. Li and S. Y. Hui, "Topology-transition control for wide-input-voltage-range efficiency improvement and fast current regulation in automotive LED applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 7, pp. 5883–5893, Jul. 2017.

- [16] M. He, F. Zhang, J. Xu, P. Yang and T. Yan, "High-efficiency two-switch tri-state buck-boost power factor correction converter with fast dynamic response and low-inductor current ripple," *IET Power Electron.*, vol. 6, no. 8, pp. 1544–1554, Sep. 2013.

- [17] M. Veerachary, Vasudha Khubchandani, "Control of switching capacitor based buck-boost converter," in *Proc. IEEE International Power Electronics Conference (IPEC)*, pp. 1–6, 2018.

- [18] K. I. Hwu, Y. T. Yau, "A KY boost converter," *IEEE Trans. on Power Electron.*, vol. 25, no. 11, pp. 2699–2703, Nov. 2010

- [19] K. I. Hwu, T. J. Peng, "A novel buck-boost converter combining KY and buck converters," *IEEE Trans. Power Electron.*, vol. 27, no. 5, pp. 2236–2241, May. 2012.

- [20] H.-S. Son, J. K. Kim, J.-B. Lee, S.-S. Moon, J.-H. Park, and S.-H. Lee, "A new buck-boost converter with low voltage stress and reduced conducting components," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7030–7038, Sep. 2017.

- [21] A. Ajami, H. Ardi and A. Farakhor, "Design, analysis and implementation of a buck-boost DC/DC converter," *IET Power Electron*. vol. 7, no. 12, pp. 2902–2913, Dec. 2014.

- [22] M. R. Banaei and H. A. F. Bonab, "A novel structure for single-switch nonisolated transformerless buck-boost DC-DC converter," *IEEE Trans. Ind. Electron.*, vol. 64, no. 1, pp. 198–205, Jan. 2017.

- [23] M. Veerachary, B. Krishnamohan, "Robust digital voltage-mode controller for fifth-order boost converter," *IEEE Trans. on Ind. Electron.*, vol. 58, no. 1, pp. 263–277, Jan. 2011.

- [24] G. F. Franklin, J. D. Powell, and A. Emami-Naeini, "Feedback control of dynamic systems," Eglewood Cliffs, NJ: Prentice-Hall, 2002, Ch-2.

- [25] MATLAB, user manual, MathWorks, 2005.

- [26] PSIM, user manual, Powersim Technologies, 2008.

- [27] dsPIC30F6010 user manual, Microchip, 2012.

Mummadi Veerachary (SM'04) was born in Survail, India, in 1968. He received the Dr. Eng. degree in electrical engineering from the University of the Ryukyus, Nakagami, Japan, in 2002. Since July 2002, he has been with the Department of Electrical Engineering, Indian Institute of Technology Delhi, New Delhi, India, where he is currently a Professor. His fields of interest are power electronics and applications, high frequency conversion systems for aerospace applications, design of

power supplies, multi-input and modular multilevel converters for degrid,control theory application, and digital and intelligent control solutions for power supplies.

Prof. Veerachary served as a Guest Editor of the *IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS*, for Special Sections on Photovoltaic Power Processing Systems and Efficient and Reliable Photovoltaic Systems. He also served as a Guest Co-Editor of the *IEEE TRANSACTIONS ON POWER ELECTRONICS* for a Special Section on Power Electronics in Photovoltaic Applications. He is currently serving as a Technical Editor for the *IEEE TRANSACTIONS ON AEROSPACE AND ELECTRONIC SYSTEMS*.

Vasudha Khubchandani received the B.Tech degree in Electrical and Electronics Engineering, SRM University, Delhi, India, in 2013 and the M.Tech degree in Power Systems from Amity University, Delhi, India, in 2016. She is currently working toward the Ph.D. degree in Department of Electrical Engineering, Indian Institute of Technology Delhi, New Delhi, India. Her research interests include modeling, analysis of power electronics systems, DC-DC converters and their control.

| TABLE II-A. COMPARISON OF OTHER BUCK-BOOST TOPOLOGIES WITH PROPOSED CONVERTER |                    |                          |                    |                                          |                              |                   |                   |                    |  |

|-------------------------------------------------------------------------------|--------------------|--------------------------|--------------------|------------------------------------------|------------------------------|-------------------|-------------------|--------------------|--|

| Converter<br>Feature                                                          | CBBC<br>[1]        | BBIF<br>[4]              | CUK<br>[2]         | TSBB<br>[6]                              | TSBBF<br>[16]                | BUBS<br>[6]       | KYBB<br>[19]      | Proposed converter |  |

| Switches                                                                      | 1                  | 1                        | 1                  | 2                                        | 4                            | 2                 | 2                 | 2                  |  |

| Diodes                                                                        | 1                  | 1                        | 1                  | 2                                        | 0                            | 2                 | 1                 | 2                  |  |

| Energy<br>storage<br>elements                                                 | 2                  | 4                        | 2                  | 2                                        | 2                            | 4                 | 5                 | 4                  |  |

| Voltage gain                                                                  | $\frac{-D}{(1-D)}$ | $\frac{-D}{(1-D)}$       | $\frac{-D}{(1-D)}$ | $\frac{D}{(1-D)}$                        | $\frac{D}{(1-D)}$            | $\frac{D}{(1-D)}$ | 2D                | $\frac{D}{(1-D)}$  |  |

| RHP Zero                                                                      | Yes                | Yes                      | Yes                | Yes                                      | Yes                          | Yes               | No                | No                 |  |

| Common ground                                                                 | NO                 | NO                       | NO                 | YES                                      | YES                          | YES               | YES               | YES                |  |

| Nature of source current                                                      | DISC.              | CONT.                    | CONT.              | DISC.                                    | DISC.                        | DISC.             | DISC.             | CONT.              |  |

| Ripple in source current                                                      | $k_{20}$           | $\frac{k_{21}DT_s}{L_1}$ | $k_{20}$           | $\left[k_{23} + \frac{k_{20}}{2}\right]$ | $\frac{-k_{2}DT_{s}}{L_{1}}$ | $(1-D)k_{20}$     | $(2I_o + k_{24})$ | k <sub>25</sub>    |  |

| Multi-mode operation                                                          | NO                 | NO                       | NO                 | Yes                                      | Yes                          | Yes               | NO                | Yes                |  |

$$\begin{aligned} k_{15} &= \left(r_2 + k_{11}\right), \quad k_{20} &= \left(V_g D T_s \big/ L_1\right), \quad k_{21} &= \left[r_{c1} i_2 - (r_1 + r_{c1}) i_1\right], \quad k_{22} &= \left(r_1 i_1 + r_{c1} i_{c1}\right), \quad k_{23} &= I_0 \big/ \big(1 - D\big), \\ k_{24} &= k_{20} \left(1 - D\right) \big(L_1 + L_2\big) \big/ 2L_2 \,, \quad k_{25} &= k_{20} \left(2L_1 + L_2\right) \big/ L_2 \,, \quad D' &= (1 - D); \text{ CONT: Continuous; DISC: Discontinuous} \end{aligned}$$

TABLE II-B. COMPARISON OF BUCK-BOOST TOPOLOGIES UNDER MULTI-MODE OPERATION

| Parameter                      | TSBB [6]           |                 | TSBBF [16] |                      |                 | BUBS[6]  |                      |          | Proposed converter |                      |                      |                      |

|--------------------------------|--------------------|-----------------|------------|----------------------|-----------------|----------|----------------------|----------|--------------------|----------------------|----------------------|----------------------|

|                                | Buck               | Boost           | Bubo       | Buck                 | Boost           | Bubo     | Buck                 | Boost    | Bubo               | Buck                 | Boost                | Bubo                 |

| No. of devices                 | 3                  | 3               | 4          | 3                    | 3               | 4        | 3                    | 3        | 4                  | 3                    | 3                    | 4                    |

| Source<br>current<br>profile   | Pulsg              | Smtw            | Pulsg      | Smtw                 | Smtw            | Smtw     | Pulsg                | Smtw     | Pulsg              | Smtw                 | Smtw                 | Smtw                 |

| Load side capacitor ripples    | $\frac{k_{31}}{L}$ | k <sub>32</sub> | $k_{32}$   | $\frac{k_{31}}{L_2}$ | k <sub>32</sub> | $k_{32}$ | $\frac{k_{31}}{L_2}$ | $k_{32}$ | $k_{32}$           | $\frac{k_{31}}{L_2}$ | $\frac{k_{31}}{L_2}$ | $\frac{k_{31}}{L_2}$ |

| Source ripple                  | High               | Low             | High       | Low                  | Low             | Low      | High                 | Low      | High               | Low                  | Low                  | Low                  |

| Switch S <sub>1</sub>          | $V_{g}$            | 0               | $V_{g}$    | $V_{g}$              | 0               | $V_{g}$  | $V_{g}$              | 0        | $V_{g}$            | $V_{c1}$             | $V_{c1}$             | $V_{c1}$             |

| Volt.<br>stress S <sub>2</sub> | $V_0$              | $V_0$           | $V_0$      | $V_0$                | $V_0$           | $V_0$    | $V_0$                | $V_0$    | $V_0$              | $V_{c1}$             | 0                    | $V_{c1}$             |

Bubo: Buck-Boost; Pulsg: Pulsating; Smtw: Smooth waveform;  $k_{3l} = v_0 D'/f_s$ ;  $k_{32} = ((I_0/D') + (k_{3l}/2L_2))$